超线程/超标量/超级流水线

Contents

超线程技术 Hyper-Threading

超线程是Intel专有的同步多线程(SMT)的实现。

每个单位时间内,CPU只能处理一个线程(Thread)。除非有两个核心处理单元,否则要想在单位时间内处理超过一个的线程是不可能的。

超线程HT(Hyper-Threading)技术是在单个核心处理单元中集成两个逻辑处理单元,也就是一个实体内核(共享的运算单元),两个逻辑内核(有各自独立的处理器状态),在一颗CPU同时执行多个程序而共同分享一颗CPU内的资源,理论上要像两颗CPU一样在同一时间执行两个线程,P4处理器需要多加入一个Logical CPU Pointer(逻辑处理单元)。因此新一代的P4 的面积比以往的P4增大了5%。而其余部分如ALU(整数运算单元)、FPU(浮点运算单元)、L2 Cache(二级缓存)则保持不变,这些部分是被分享的。

虽然采用超线程技术能同时执行两个线程,但它并不象两个真正的CPU那样,每各CPU都具有独立的资源。当两个线程都同时需要某一个资源时,其中一个要暂时停止,并让出资源,直到这些资源闲置后才能继续。因此超线程的性能并不等于两颗CPU的性能。

SMT

simultaneous multithreading technology

同步多线程(Simultaneous multithreading, SMT)是一种使用硬件多线程提高超标量cpu总体效率的技术。SMT允许多个独立的执行线程更好地利用现代处理器体系结构提供的资源。

缺点

2013年,英特尔放弃了SMT技术,转而采用乱序执行的Silvermont处理器内核,因为他们发现,与使用较少的SMT内核相比,乱序执行(out-of-order execution)能提供更好的性能和更高的能效。

本质

超线程通过复制处理器的某些部分(存储体系结构状态的部分)来工作,但不复制主要执行资源。 该技术对操作系统和程序透明。充分利用超线程所需的最低要求是操作系统中的对称多处理(SMP)支持,因为逻辑处理器显示为标准的独立处理器。 在多处理器超线程系统上优化操作系统行为是可能的。例如,考虑一个具有两个物理处理器的SMP系统,它们都是超线程的(总共有四个逻辑处理器)。如果操作系统的线程调度程序不知道超线程,它将对所有四个逻辑处理器一视同仁。如果只有两个线程有资格运行,它可能会选择在恰好属于同一物理处理器的两个逻辑处理器上调度这些线程;当另一个处理器空闲时,另一个处理器会变得非常繁忙,这会导致性能下降,而不是将线程调度到不同的物理处理器上。通过改进调度器,将逻辑处理器与物理处理器区别对待,可以避免这个问题;从某种意义上说,这是NUMA系统所需的一种有限形式的调度器更改。

The main function of hyper-threading is to increase the number of independent instructions in the pipeline; it takes advantage of superscalar architecture, in which multiple instructions operate on separate data in parallel. 超线程的主要功能是增加流水线中独立指令的数量;它利用了超标量体系结构的优势,即多条指令并行地对不同的数据进行操作。

个人理解:

- 所以超线程的本质是在一套流水线中增加部分指令,比如多加个ALU,使得有两个ALU,这样在其中一个忙碌的时候就可以直接用另一个。

- 由于超线程技术对操作系统和程序透明,所以可以实现一个物理cpu核心中跑两个内核级线程。

图解

in cs252

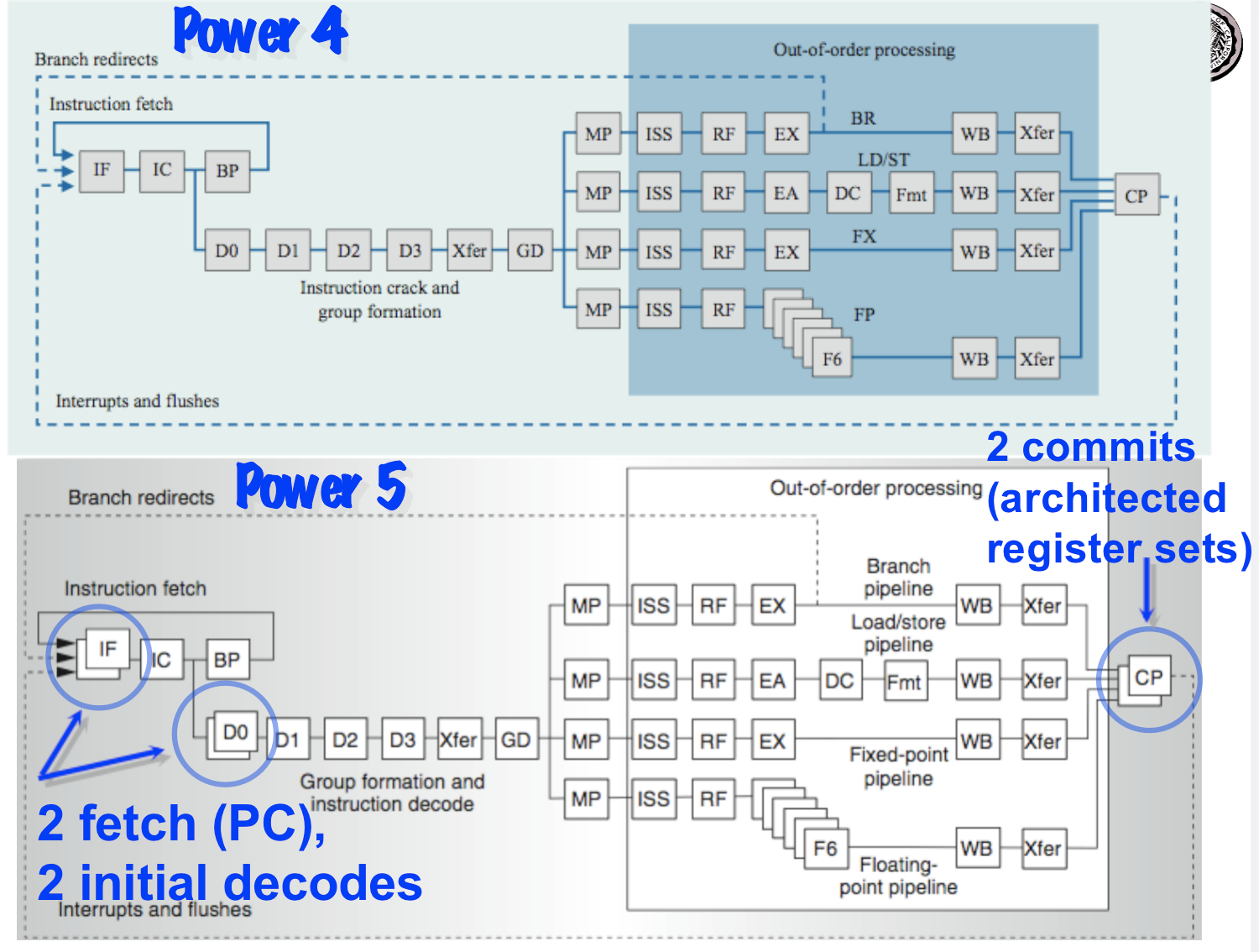

图中Power5实现了SMT,Power4没有

Power4

Single-threaded predecessor to Power 5. 8 execution units in out-of-order engine, each may issue an instruction each cycle Power4是Power5的单线程前身。乱序引擎中有8个执行单元,每个执行单元每个周期都可以发射一条指令。

Power5

Changes in Power 5 to support SMT:

Increased associativity of L1 instruction cache and the instruction address translation buffers Added per thread load and store queues Increased size of the L2 (1.92 vs. 1.44 MB) and L3 caches Added separate instruction prefetch and buffering per thread Increased the number of virtual registers from 152 to 240 Increased the size of several issue queues The Power5 core is about 24% larger than the Power4 core because of the addition of SMT support

in wiki

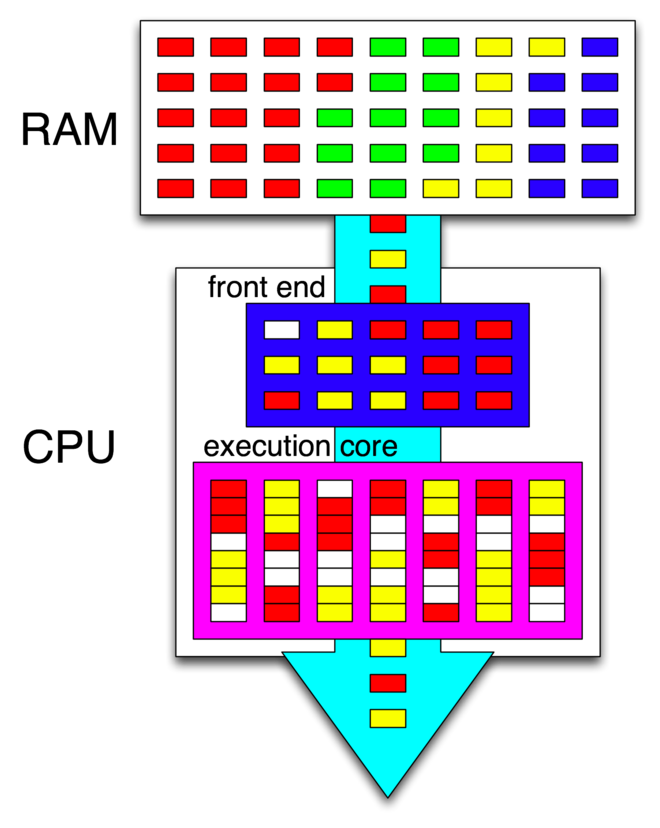

In this high-level depiction of HTT, instructions are fetched from RAM (differently colored boxes represent the instructions of four different processes), decoded and reordered by the front end (white boxes represent pipeline bubbles), and passed to the execution core capable of executing instructions from two different programs during the same clock cycle.

In this high-level depiction of HTT, instructions are fetched from RAM (differently colored boxes represent the instructions of four different processes), decoded and reordered by the front end (white boxes represent pipeline bubbles), and passed to the execution core capable of executing instructions from two different programs during the same clock cycle.

相关讨论

https://www.reddit.com/r/hardware/comments/143ew5/what_is_the_difference_between_hyperthreading_and/

超标量(Super Scalar)

wiki Superscalar_processor

超级标量机主要是借助硬件资源重复(例如有两套译码器和ALU等)来实现空间的并行

操作.

相关文章

https://www.slideshare.net/ishaqahmad3154/superscalar-superpipeline-processor Pipelining, Superscalar, Multiprocessors

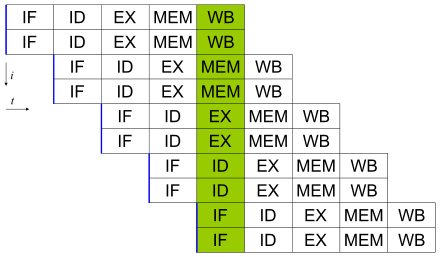

流水线增强了超标量能力 (pipelining augmented with superscalar capability)

超标量CPU设计强调提高指令分配器的准确性,并使其始终保持多个执行单元处于使用状态。随着单元数量的增加,这一点变得越来越重要。早期的超标量CPU具有两个ALU和一个FPU,而后来的设计(如PowerPC 970)则包括四个ALU,两个FPU和两个SIMD单元。如果调度员不能有效地使所有这些单元接收指令,那么系统的性能将不会比简单,便宜的设计好。

在一个标量CPU中,调度器从内存中读取指令,并决定哪些指令可以并行运行,将每个指令分派给包含在单个CPU中的多个执行单元中的一个。因此,可以设想一个超标量处理器拥有多个并行管道(流水线),每个管道(流水线)同时处理来自单个指令线程的指令

超标量依赖指令级并行(Instruction level parallelism)

超级流水线(Super Pipeline)

csdn 超级流水线又叫做深度流水线,它是提高cpu速度通常采取的一种技术。CPU处理指令 是通过Clock来驱动的,每个clock完成一级流水线操作。每个周期所做的操作越少,那么 需要的时间久越短,时间越短,频率就可以提得越高。所以超级流水线就是将cpu处理 指令是得操作进一步细分,增加流水线级数来提高频率。频率高了,当流水线开足马力 运行时平均每个周期完成一条指令(单发射情况下),这样cpu处理得速度久提高了。 当然,这是理想情况下,一般是流水线级数越多,重叠执行的执行就越多,那么发生 竞争冲突得可能性就越大,对流水线性能有一定影响。 现在很多cpu都是将超标量和超级流水线技术一起使用,例如pentium IV,流水线达 到20级,频率最快已经超过3GHZ.我们教科书上用于教学的经典MIPS只有5级流水。 nature:增加流水线级数

other

https://www.reddit.com/r/hardware/comments/143ew5/what_is_the_difference_between_hyperthreading_and/

Author sorvik

LastMod 2020-12-27